- Cisco Community

- Technology and Support

- Data Center and Cloud

- Storage Networking

- FCP ISL theoretical question

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

03-01-2012 02:32 AM

Hi,

I' ve got a theoretical question about the behaviour of ISL at Cisco MDS switches:

I heard, that during a transfer (a continuous sequence of frames) between a target and an initiator (each of them are on seperated switches, which are connected with only one ISL), no other end device can use the ISL. When the sequence of frames (same OX ID, RX ID) is transfered, another end device can use the ISL.

There is no "multiplexing" of the ISL.

Q1: Is this true?

Q2: If yes, what happend, if you tranfer a lot of data between one target & one initiator. Is there a congestion on the isl for all other devices?

Regards

Markus

Solved! Go to Solution.

- Labels:

-

Storage Networking

Accepted Solutions

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

03-01-2012 12:37 PM

Markus,

The MDS doesn't transfer entire exchanges at a time on a given ISL. Meaning OXID1, OXID2 etc... It will transmit the frames as they arrive. Such that you could transfer over the ISL:

OXID1Frame1, OXID2Frame1, OXID1Frame2, OXID1Frame3

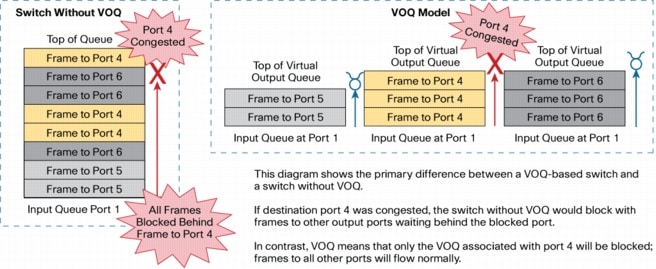

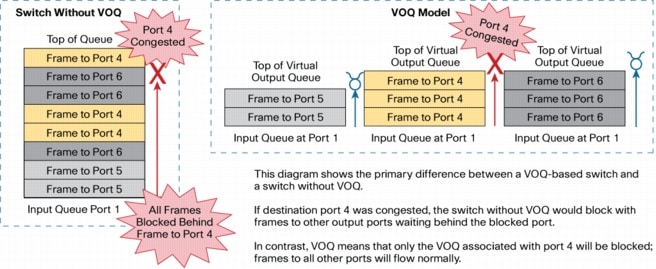

The second problem could occur in a situation in which the receiver's buffers were full and thereby the TX port on the switch egress frames out of the switch, then the Virtual Output Queue could fill up (for which there is one assigned to every input port for every output port) and eventually the TX side of the ISL would run out of buffers. To completely avoid this, you would need per flow buffer 2 buffer credits. As a note the number of and depth of VOQ was designed to help avoid this situation as explained in this whitepaper and illustrated below.

-Seth

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

03-01-2012 12:37 PM

Markus,

The MDS doesn't transfer entire exchanges at a time on a given ISL. Meaning OXID1, OXID2 etc... It will transmit the frames as they arrive. Such that you could transfer over the ISL:

OXID1Frame1, OXID2Frame1, OXID1Frame2, OXID1Frame3

The second problem could occur in a situation in which the receiver's buffers were full and thereby the TX port on the switch egress frames out of the switch, then the Virtual Output Queue could fill up (for which there is one assigned to every input port for every output port) and eventually the TX side of the ISL would run out of buffers. To completely avoid this, you would need per flow buffer 2 buffer credits. As a note the number of and depth of VOQ was designed to help avoid this situation as explained in this whitepaper and illustrated below.

-Seth

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

03-01-2012 01:05 PM

Thanks, that was what I want to heard... I read this in an article and was not sure about this behaviour.

Regards Markus

Discover and save your favorite ideas. Come back to expert answers, step-by-step guides, recent topics, and more.

New here? Get started with these tips. How to use Community New member guide